반응형

아래는 ARMv8 A 기준 스펙 문서이다.

https://developer.arm.com/documentation/ddi0487/latest

Documentation – Arm Developer

developer.arm.com

ARM Register

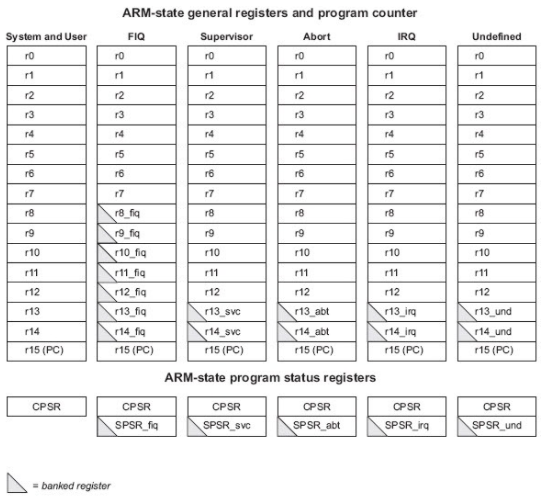

아래 표는 ARM 아키텍처에서 사용되는 Register 이다.

실제 예전에 히언님의 쓰신 Embedded Recipe 를 보며 도움이 많이 되었던 내용이기도 하다.

아래 내용을 모르면 ARM 에 모른다고 봐도 무방할 정도이다.

System and User FIQ Supervisor Avort IRQ 등 각 모드별로 사용 되는 Register 들이 조금씩

다르다. 공통으로 사용되는 Register 가 있는 반면, 그 목적에 맞게 다르게 사용되는

Register 도 있다.

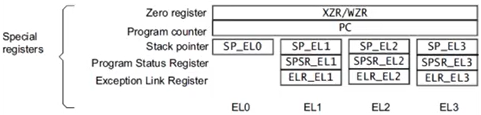

스페셜 레지스터

이 중 Special Register 라고 하여 주요 깊게 볼 register 들이 있다.

- 가장 중요한 특징으로 원활한 컨텍스트 스위칭을 위해 설계됨

- 익셉션 레벨 별로 접근됨

Stack Pointer Register

- t thread : 모든 Exception Level 에서 SP_EL0 만을 사용

- h handler : 각 Exception Level 에서 SP_ELx 를 사용

Stack Pointer Select Register (SPSel)

- 0 : 모든 Exception Level 에서 SP_EL0 사용

1 : 모든 Exception Level 에서 각자의 SP_ELx 를 사용 - Reset Default 는 1값

Program Counter

컴퓨터와 구조 OS 시간에 많이들 들어봤을 것이다. 현재 실행중인 상태 저장을 위한 Register 이다.

- ARMv7 에서는 PC 가 일반 레지스터

- ARMv8 에서는 PC 또한 스페셜 레지스터로 간주

- 즉, PC 에 직접 접근이 불가

Exception Link Register ELR_ELx

- Exception Return Address 를 저장

SPSR Register(Saved Program Status Register)

- 익셉션이 유발될 시점의 PState 값을 백업 (PSTATE 는 프로세스의 상태를 의미)

- 익셉션 레벨별로 존재

- 익셉션을 처리한 다음에 복귀할때 재설정

아래와 같이 모드 별로 존재한다.

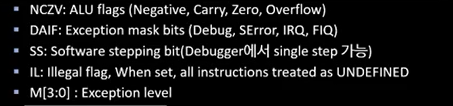

SPSR 을 자세히 보면 아래의 구조로 되어있다. 간단히 아래 의 역활을 하며, 자세한 내용은 스펙문서를 참고하면 된다.

익셉션이 일어날때 처리 과정은 아래 그림과 같다.

보통 eret 명령어가 실행되면, SPSR 레지스터의 값이 PSTATE 로 변경된다.

리눅스 커널또한 ARM 아키텍처 기반의 오픈소스 이며,

대부분 펌웨어 임베디드 레벨에서 사용 중이라고 보면 된다.

반응형

'Embedded > Arm 아키텍처' 카테고리의 다른 글

| [Arm 아키텍처] AAPCS(Calling Convention) (0) | 2022.02.19 |

|---|